미세화 한계, 미세화 이후 공정연구 돌입

■ 초고집적 반도체 소재 기술

반도체분야는 신소재 채택측면에서는 매우 보수적인 입장을 견지해왔다. 실리콘, 질소, 산소 그리고 Al, W, Co, Ni, Cu, Ta, Ti 정도의 물질과 Arsenic, Phosphorus등의 dopant등 한정된 원소만을 이용하여 수십 년간 반도체 소자를 작게 만들면서 발생하는 문제들을 해결해 왔다. 최근에는 새로운 소재, 공정들이 속속 적용되고 있고, 신소재를 적용하는 데 필요한 경험이 축적되면서 새로운 소재의 적용주기도 빨라지고 있는 측면도 있기만, 그만큼 기술적 난관을 돌파하기 어려워지고 있어서 절박한 상황에서 충분한 검증없이 적용되고 있다고 생각해볼 수도 있다. 신소재기술의 경우, 반도체 소자에 요구되는 성능을 모두 만족하는 성능을 갖춘 소재를 개발하는 것이 매우 어렵기 때문에, 향후 소자기술의 한계는 아래에 설명하는 소재의 한계에 의해 결정된다고 볼 수 있을 것이다.

1990년대 초반부터 약 20년간 금속배선 부분에 사용되던 SiO2를 저유전절연체로 대체하기 위한 대규모 국제연구가 진행되었으나, 전기적 유전율, 신뢰성 뿐 아니라 열팽창계수 등을 포함한 구조적문제, 방열문제 등의 요구조건을 만족시킬 수 있는 신소재를 찾는 것이 어려웠기 때문에 유전율이 2.2정도인 SiOCH 수준에서 더 이상 개선이 어렵게 되었다.

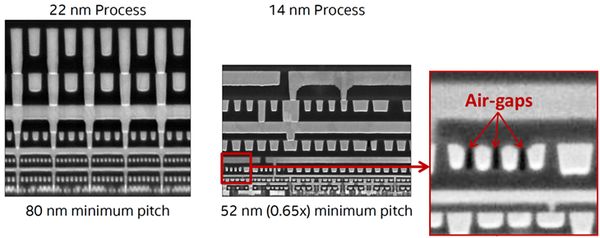

이 때문에 <그림 3-3-1-7>에 보인 것과 같이 유전율 1를 가지는 air gap을 배선 구조내에 형성하여 유효유전율을 낮추는 방향으로 전략을 바꿔, 소재보다는 집적공정을 개선하는 방향으로 연구가 진행되고 있다. 하지만, 이 방법은 배선기술의 미세화를 제한하는 요인이 되고 있다. 최근에는 소모전력의 대부분이 배선부분의 정전용량에 비례하여 발생하기 때문에, 소자의 소모전력을 최소화하기위해서는 공기와 유사한 유전율을 가지면서도 실리콘 산화막과 유사한 구조적 강도를 갖는 소재를 개발할 필요가 있다.

또 다른 사례로 2000년대 초반 90nm급 기술에서부터는 금속배선간의 절연막뿐만 아니라 배선금속을 Al (2.67μΩ-cm) 에서 Cu(1.67μΩ-cm)로 바꾸게 되었다. Cu는 실리콘 내에서의 확산속도가 매우 높고, midgap 결함을 만들기 때문에 대표적인 기피대상 소재였지만, electron migration문제에 대한 내성이 좋고, Al 대비 전도도가 훨씬 높아서, Cu 배선소재가 실리콘 기판으로 확산하지 않도록 하는 barrier소재 TiN, TaN 등과 함께 채택되었다. 그러나 Cu 배선기술도 소자의 미세화가 계속되면서 저항의 한계에 도달하여 단결정구조를 이용하여 저항을 더 낮추거나, barrier 소재의 두께를 줄여서 유효 Cu 배선의 두께를 늘리는 등 최적화 연구가 계속 되고 있지만, 역시 소자의 요구사항을 만족하지 못하는 수준에서 개발이 정체되고 있다. 그래핀 나노리본 또는 Graphite/Cu 적층소재 등 대체소재에 대한 연구도 진행되고 있지만, 아직 기술성숙도는 충분하지 않는 수준이어서 기술혁신이 시급한 분야이다.

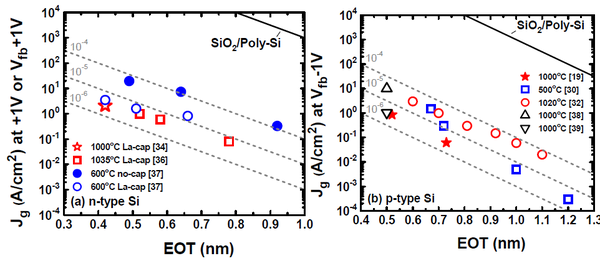

2007년 인텔을 필두로 반도체소자에 Hafnium기반 고유전절연막이 추가되고 TiN, TaAlN등 금속전극이 적용되기 시작했다. 금속전극은 TaN, TiN기반에 Al, Si doping을 통해 유효일함수를 조절하고 있으며, 금속의 grain boundary 제어를 통해 일함수를 균일하게 하는 등의 연구는 진행되고 있으나, 게이트스택부분에서는 기존 Hafnium 기반 고유전절연막의 두께를 줄이는 방법으로 미세화가 진행되고 있고, <그림3-3-1-8>에 보인 것과 같이 다양한 방법으로 미세화가 가능한 상황이어서 새로운 소재에 대한 수요는 많지 않다. 고유전절연막의 경우 결정구조 제어를 통해 유전율을 ~20에서 ~40까지 높이는 것이 가능하다는 사례가 보고되고 있으나 기술성숙도는 낮은 편이다.

Silicon 채널소재를 대체하기 위한 노력은 40년 이상 계속되어 왔고, 2000년대 초반부터는 Ge 또는 GaAs기반 화합물반도체를 사용하기 위한 연구가 본격화되었다. Ge은 1960년대에 bandgap이 작고, 열적안정성이 좋지 않아서 폐기되었던 기술인데, 소자동작전압이 낮아짐에 따라 다시 활용가능성이 검토되고 있고, strain engineering을 위해 source/drain에 SiGe 이 이미 도입되어있어서 진입장벽은 높지 않은 수준이다. 화합물반도체는 소자이동도가 매우 높아서 사용가능성에 대한 연구가 1970년대부터 꾸준히 진행되어왔고, HEMT소자 등 특수분야에 적용되는 기술도 개발되었으나, MOSFET구조에 꼭 필요한 게이트 절연막을 개발하지 못하는 것이 문제였다.

최근 ALD기반의 고유전절연막 증착기술이 채용되면서 게이트 절연막 형성 문제를 극복할 수 있을 것으로 생각했으나, 아직 contact 저항 문제 등 근본적인 문제가 해결되지 않아 전면적인 적용이 지연되고 있다. 인텔은 22nm급 소자에서부터 적용가능성을 시사해왔으나, 7nm급 소자에서도 아직 채용되지 않고 있으며, 향후 gate all around (GAA)소자가 적용될 것으로 예상되고 있는 5nm급 이후에는 SiGe 희생층과의 선택적 epi 및 식각공정이 어려워서 insertion point를 놓치고 있는 것으로 보여진다.

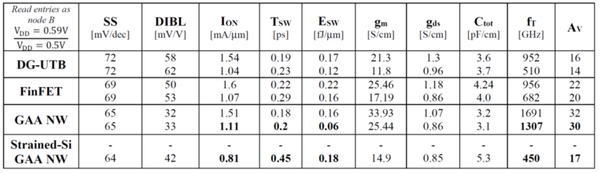

<그림 3-3-1-9>는 다양한 소자구조에서 III-V 소자를 만들었을 경우, Interface와 contact 저항이 최상의 수준에 도달할 수 있으리라는 가정하에 소자의 성능을 시뮬레이션한 결과이다. GAA소자구조에서 가장 높은 동작속도를 얻을 수 이었지만, roadmap target을 만족하지는 못했다. <그림 3-3-1-10>은 좀 더 비관적인 결과를 보여준다. 이론적으로 SiGe을 사용할 경우, 나노Ω급의 접촉저항을 달성할 수 있으나, InGaAs 의 경우 <그림 3-3-1-6(b)>에 보인 것과 같이 이론적인 연구로도 10나노옴 이하로 접촉저항을 줄이는 것이 어려울 것으로 예측되고 있다.

차세대 반도체 기술의 개발성과는 위에 언급한 것과 같이 배선절연막, 배선소재, 접촉저항소재 등의 개발성과에 의해 결정될 것으로 생각되어 그 중요성은 아무리 강조해도 지나치지 않을 것이다.

EUV 공정단순화 개발기간 단축 큰 장점

EUV 도입, 소자레벨·시스템레벨 개선 必

■ 초고집적 반도체 공정기술 동향

1, 2장에서 언급한 바와 같이 차세대 반도체 기술은 미세화의 한계에 도달해가고 있다. 따라서 미세화경쟁과 더불어 미세화 이후의 기술을 구현하기 위한 공정도 연구해야할 단계이다. 그러나, 현재 산업계에서는 미세화 기술과 관련된 연구에 집중하고 있기 때문에 소자연구와 직접적인 관련이 있고, 최근 활발히 연구되고 있는 공정 중 일부를 발췌하여 소개하고자 한다.

가) EUV 노광공정

EUV는 기술은 13.5nm의 단파장을 사용하여 미세패턴을 형성하는 기술이다. 아래 critical dimension (CD) 을 정의하는 수식에서 볼수 있는 변수들을 제어하여 미세패턴을 형성할 수 있다.

k는 공정변수이고 이론적으로 0.25가 한계이지만, 대략 0.3-0.4정도의 값을 갖고 있다. NA (numerical aperture)는 약 0.9정도이다. 따라서, 얼마나 작은 패턴을 형성할 수 있는 지는 파장에 의해 결정되는 데, EUV 광원은 13.5nm의 파장을 사용하고 있다. ArF레이저의 193nm에 비교하더라도 EUV 노광공정의 장점은 분명하다.

EUV 노광기술은 기술의 장점이 문제가 아니라, EUV 장비의 구현과 비용대비 효율성을 확보하는 것이 어려워서 30년 이상 장기간의 개발과정을 거쳐 최근 상용화단계에 근접한 상황이다. EUV 기술개발에서 가장 난제였던 광원기술은 꾸준히 발전되어 최근에는 125W 수준에 도달해있다 (개발목표 250W, 125 웨이퍼/hour). EUV 레티클을 보호하는 펠리클은 EUV 투과도가 높은 대면적 멤브레인 박막을 활용해야하는데, 박막의 열적안정성이 충분하지 않고, 목표투과도를 갖는 박막의 기계적 안정성을 확보하지 못한 상태이다.

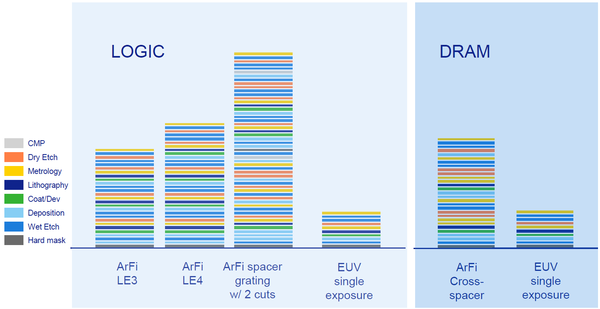

초장기 개발기간과 기술적 난제에도 불구하고 EUV 개발이 꾸준히 진행되고 온 것은 미세패턴을 만들기 위해 사용되고 있는 노광공정이 하나의 패턴을 만들기 위해 다중공정을 거쳐야할 정도로 복잡해지면서 공정비용이 급격히 증가하고 있기 때문이다. <그림 3-3-1-11>에 보인 것과 같이 EUV 공정을 사용하면 공정단순화로 인해 7nm기술의 경우 공정비용이 12%정도 절감되고 수율은 9% 로 개선될 수 있다는 것이 EUV 기술의 장점이다. 간접적인 효과이지만, 공정단순화로 개발기간이 단축되는 것도 매우 큰 장점이다.

나) Selective hetero-epitaxial 공정

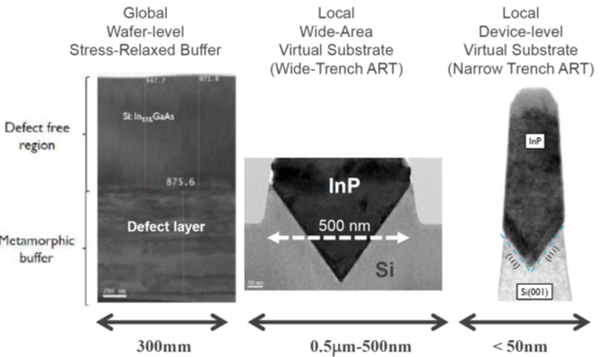

EUV가 도입되고 나면 소자의 미세화 자체 보다는 미세화에 따른 문제점을 해결하고, 목표로 하는 시스템 성능을 확보할 수 있는 지에 대해 소자레벨, 시스템레벨에서의 개선이 필요하다. 앞에서 제시한 여러 소자 기술들을 구현하고, 성능을 개선하기 위해서는 소자의 일부분에 실리콘과 다른 이종소재를 성장시키거나. 칩의 일부영역에 실리콘과 다른 소재를 성장시키는 선택적 헤테로 에피텍시 기술이 필요하다. <그림 3-3-1-12>은 성장면적별로 구분하여 다양한 선택적 결정기판 성장이 가능하다는 것을 보여준다.

이 공정을 이용하여 앞에서 언급된 source 영역에 화합물반도체를 적용한 tunnel FET 제작도 가능하다. 특히 <그림 3-3-1-13>에 보인 것과 같이 기판상에 존재하는 seed 영역을 template로 사용하여 시작되는 template assisted selective epitaxy (TASE) 공정을 사용할 경우, 매우 다양한 소재를 복합적으로 사용한 소자 제작이 가능하다.

<그림 3-3-1-14>는 template assisted selective epitaxy공정을 이용하여 InAs, GaSb, Si 를 단일소자내에서 조합한 헤테로 에피텍시 tFET을 보여주고 있다. 현재 기술수준은 단일소자의 구조를 구현하는 정도이며, 아직 소자성능을 검증할 수준에 도달해있지는 않기 때문에 5nm급 소자에 적용가능한 수준이 되려면 소자성능은 물론 각 소재별로 접촉저항은 나노Ω급으로 낮출 수 있는 기술도 확보되어야한다.

다) Atomic layer etching (ALE) 공정

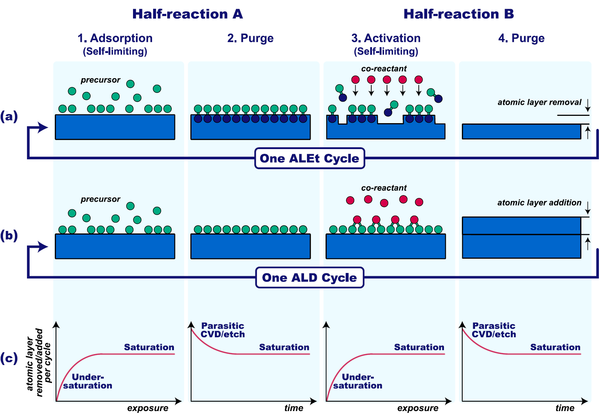

FinFET, GAA 소자등 복잡한 3차원 구조를 가진 소자들이 적용되면서, 비평면 구조에 다양한 소재를 등방성을 가지고 증착하는 atomic layer deposition 공정뿐 아니라 3차원 등방식각이 가능하고, gas flow의 영향을 덜 받는 atomic layer etching 공정의 중요성이 부각되고 있다. <그림 3-3-1-15>은 ALD 공정과의 유사성을 비교하여 ALE공정의 원리를 설명하는 모식도이다. ALE 공정중 adsorption되는 영역을 photo activation등의 방법으로 조절하면 매우 높은 선택비를 갖는 부분적 이방성 식각도 가능하다.

다만, ALD 공정과 마찬가지로 layer by layer 공정을 사용하기 때문에 생산성이 낮다는 점이 한계로 지적되고 있다. 20년 이상 연구되어온 ALD 공정이 최근 양산에 적용되기 시작한 것에 비교한다면, 상용화단계까지 아직 보완이 많이 필요할 것이다. 다만, layer by layer 공정의 양산효율을 제고하는 데 필요한 경험이 이미 많이 축적되어 있기 때문에 3차원 소자 집적공정에 적용할 수 있을 것으로 기대된다.

▲ <그림 3-3-1-7>인텔의 BEOL 배선 구조(2014)

▲ <그림 3-3-1-7>인텔의 BEOL 배선 구조(2014) ▲ <그림 3-3-1-8>La2O3 capping층의 oxygen 흡수효과를 이용한 HfO2 절연막의 scaling 한계

▲ <그림 3-3-1-8>La2O3 capping층의 oxygen 흡수효과를 이용한 HfO2 절연막의 scaling 한계 ▲ <그림 3-3-1-9>다양한 소자구조에서 III-V MOSFET 모델링 결과

▲ <그림 3-3-1-9>다양한 소자구조에서 III-V MOSFET 모델링 결과 ▲ <그림 3-3-1-11>EUV 공정을 이용한 공정단순화

▲ <그림 3-3-1-11>EUV 공정을 이용한 공정단순화 ▲ <그림 3-3-1-12>다양한 스케일에서의 epitaxial 공정결과

▲ <그림 3-3-1-12>다양한 스케일에서의 epitaxial 공정결과 ▲ <그림 3-3-1-15>Atomic layer deposition과 etching 공정의 개념 모식도

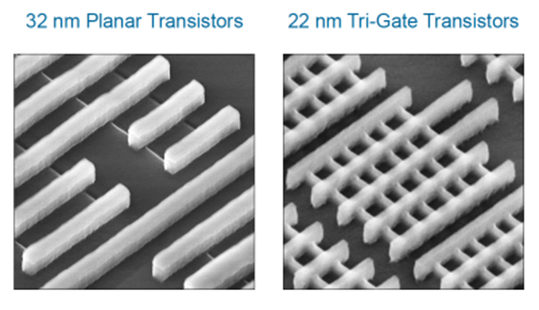

▲ <그림 3-3-1-15>Atomic layer deposition과 etching 공정의 개념 모식도 ▲ <그림 3-3-1-1>32nm급 소자와 22nm급 소자구조의 변화

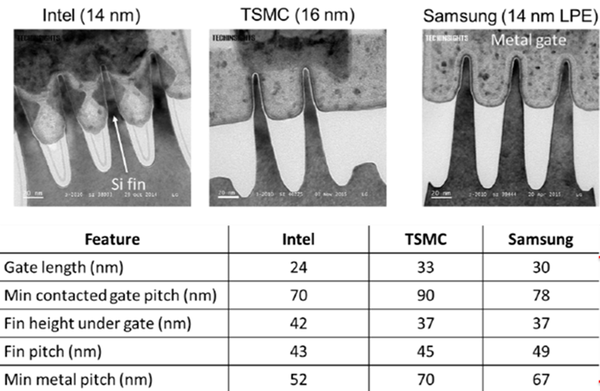

▲ <그림 3-3-1-1>32nm급 소자와 22nm급 소자구조의 변화 ▲ <그림 3-3-1-2>14nm 급 소자의 단면구조 및 주요 dimension parameters

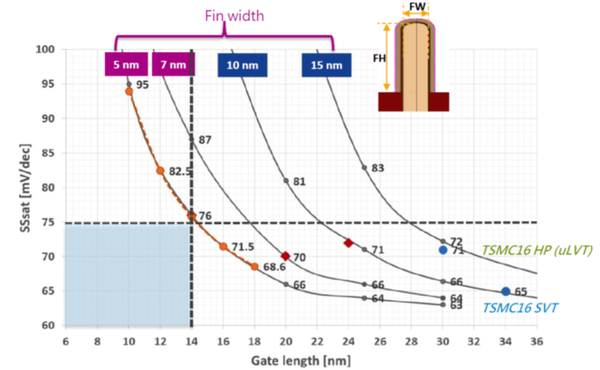

▲ <그림 3-3-1-2>14nm 급 소자의 단면구조 및 주요 dimension parameters ▲ <그림 3-3-1-3>fin의 두께에 따른 소자 특성 개선 추세

▲ <그림 3-3-1-3>fin의 두께에 따른 소자 특성 개선 추세