메모리 초격차 유지, 시스템반도체 기술 개발 시급

■ 기술개요

초고집적 반도체 기술을 굳이 종합적인 반도체기술과 구분하여 정의하자면, 기술경쟁의 최첨단에 해당하는 로직반도체, 메모리반도체 및 기타 특수 반도체 기술이라고 한정해볼 수 있을 것이다. 그중에서도 이 장에서는 현재 적용되고 있는 기술 또는 1-2 세대이내 적용하기 위해 연구되고 있는 반도체 기술로 논의의 범위를 한정하고, 핵심소자기술의 발전방향을 중심으로 하여 관련 소재, 공정, 집적기술 및 시스템 기술 분야에서의 대표적인 도전과제와 대응전략에 대해 대략적인 현황을 정리해보고자 한다. 이렇게 논의대상 및 범위를 제한한다고 해도, 매우 광범위한 분야이기 때문에, 아쉽지만 최근 학회에 보고된 결과들을 중심으로 주요 결과들을 간단히 제시하는 수준에 머무를 수 밖에 없는 한계가 있을 것이므로, 심도있는 정보를 필요로 하는 독자들은 참고문헌을 활용할 것을 부탁드린다.

■ 연구개발 동향

반도체기술은 ITRS 로드맵을 기반으로 선행기술에 대한 공동의 목표를 설정하고, SEMATECH, IMEC등 국제공동연구기관을 활용하여, 개발비용이 많이 드는 노광공정, Cu 배선, 300mm, 450mm 장비개발, 게이트스택기술 등 선행공정/장비를 초기단계에서 양산이전 수준까지 공동으로 개발함으로써 개발비용부담을 경감해왔다. 최근에는 SEMATECH이 없어지고, IMEC이 공동연구의 중심역할을 하고 있으나, 기업들에게 필요한 단기연구중심의 과제를 수행하고 있어서, 중장기 연구를 공동으로 수행하는 기능이 없어진 상태이다.

ITRS 로드맵이 선행공정에 대한 가이드라인을 제시하는 기능을 상실하게 된 것은 중장기 연구를 수행할 수 있는 공감대를 형성할 수 있는 기관이 없어지고, 기술개발의 난이도가 높아지면서, 단기 기술목표를 해결하기 위한 기술이 다변화되는 상황 때문이다. 이로 인해 중장기기술전망보다는 시스템 기술에 대한 전망을 포괄하는 International Roadmap for Devices and Systems (irds.ieee.org)가 새롭게 구성되었다.

IDRS는 Application Benchmarking, System and Architecture, More Moore, Beyond CMOS, Packing Integration, Outside System Connectivity, Factory Integration, Lithography, Metrology, Emerging Research Materials, Environment, Health, and Safety, and Yield 등의 분야로 구성되어 있고, 다음과 같은 EU, 일본의 roadmap 프로그램 및 관련 기관들이 참여하고 있다.

● Nano Electronics Roadmap for Europe: Identification and Dissemination” (NEREID)

● The System Device Roadmap Committee of Japan (SDRJ)

● ITRS 2.0

● the International Electronics Manufacturing Initiative (iNEMI)

● Sandia National Labs

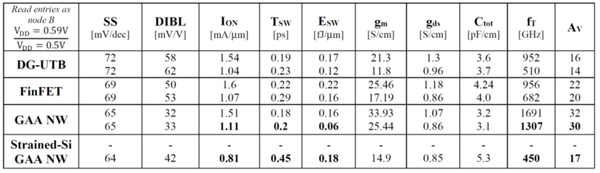

IDRS는 2016년 1차 백서(white paper)를 내고, 차세대 기술의 문제점들의 현황에 대해 보고한 바 있는 데, 상세보고서는 www.irds.ieee.org/reports에서 볼 수 있다. <표 3-3-1-1>은 현재 기술을 연장하기 위해 필요한 more moore기술 목표가 정리되어 있다. 본 보고서에 언급한 바와 같이 FinFET → GAA → vertical GAA → M3D 순으로 차세대 기술목표가 설정되어 있으나, 실제 구현에 필요한 단위기술의 성숙도는 2021년이후로 매우 낮게 평가되어 있다. 산업계에서 이 문제를 해결하고 미세화 위주의 기술을 계속 사용하게 될지, 아니면 향후 5년 이내에 반도체 기술의 패러다임 전환의 계기가 마련될 지는 주목해서 지켜봐야할 상황이다.

미국, EU, 일본, 중국은 각각의 처한 상황에 따라 독자적인 대응책을 제시하고 있는 데, 이를 <표 3-3-1-2>에 간략히 요약해보았다. 미국, EU, 중국 등에서는 공격적인 투자를 시작했고, 국내에서도 차세대 반도체 기술개발에 선행연구 프로그램이 시작된 데 반해 일본에서는 매우 제한적인 수준의 투자만 진행되고 있다는 것이 특징이라고 할 수 있다.

다음에는 반도체 소자, 소재, 공정기술, 집적기술, 패키징기술의 순으로 주요 기술 개발 현황에 대해 간략히 정리했다.

■ 초고집적 반도체 소자 기술

반도체 소자는 미세화에 수반되는 단채널효과를 억제할 수 있는 방향으로 소자구조 및 소재를 최적화하면서 발전되어왔다. 1960년 강대원박사와 아탈라박사에 의해 MOSFET이 구현된 이후, 약 40년간 평면 MOSFET 구조를 유지하면서 소자미세화에 따라 발생하는 단채널효과로 인한 문제점들을 절연막의 유전율 및 질소함량최적화, source/drain junction profile, contact 저항 저감을 위한 silicide 도입등 새로운 소재 및 공정을 적용하여 해결해가면서 발전해왔다. 예를 들면 2007년 인텔(Intel)에서 처음으로 polysilicon/oxynitride 기반의 게이트절연막을 metal gate/고유전절연막으로 전환했던 이유는 단채널효과 경감을 위해 게이트절연막의 전기적 두께를 줄이는 과정에서 발생된 기존 실리콘 산화막의 신뢰성 문제가 발생하여 이 문제를 해결할 수 있는 새로운 소재가 필요했기 때문이다.

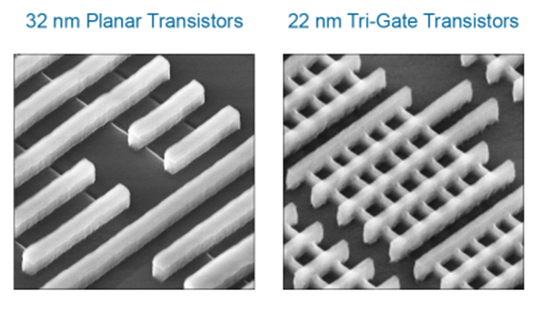

22nm급 소자부터는 소자구조가 근본적으로 변화되어 <그림 3-3-1-1>에 보인 것과 같이 전도층의 양면에 게이트를 만들 수 있는 FinFET 구조가 적용되었다. 이 경우 소자의 채널 width가 Fin의 높이에 의해 결정되기 때문에 소자구동전류가 Fin 개수의 정수배로 결정되므로, 회로설계시 많은 제약이 발생된다. 이러한 불편함에도 불구하고, FinFET구조는 단채널효과를 극단적으로 제어할 수 있다는 장점이 있어 22nm 노드부터 상용화기술로 채택되었고, 7nm급 기술까지 4세대 동안 metal gate/고유전 절연막 기반에 FinFET기술이 합쳐진 형태로 큰 변화없이 미세화에 따른 부수적인 문제들을 해결하면서 사용되어왔다.

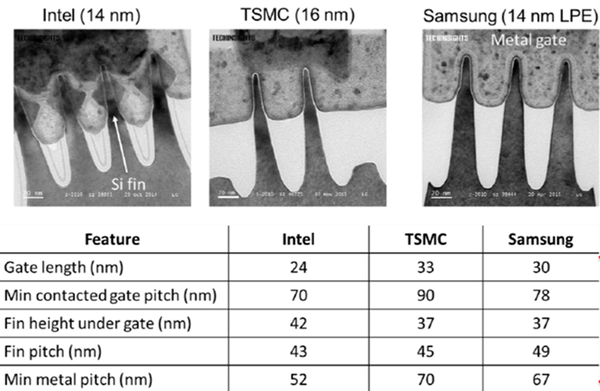

FinFET 기술에서 미세화는 게이트 길이를 줄이는 것보다는 fin의 폭을 좁혀서 게이트제어를 용이하게 하고, fin의 높이를 높여서 구동전류를 개선하는 방향으로 발전되어왔다. FinFET의 게이트 길이는 평면소자와는 달리 replacement 게이트구조를 적용하기 위해 dummy 게이트구조를 사용함에 따라, trench 구조를 metal gate/고유전 절연막으로 채우는 과정에서 공정상의 한계로 미세화가 어려워진 상태이다. <그림 3-3-1-2>는 여러 반도체 기업의 상용화제품에 적용된 게이트 구조 단면을 보여주는 데, 게이트 길이는 기술노드의 절반이 아니라, 훨씬 큰 값을 가지게 있음을 알 수 있다.

이 때문에 최근에는 미세화의 척도가 게이트 길이보다는 fin의 폭에 의해 대변된다고 할 수 있다. <그림 3-3-1-3>는 최근 기술노드에서 기술노드가 변화됨에 따라 fin의 두께가 점차 감소되고 있고, 그에 따라 단채널효과가 줄어들고, swing이 개선된다는 연구결과를 보여주고 있다. 7nm급 소자기술에 적용되는 fin의 두께는 이미 7-8 nm정도밖에 되지않는 데, 이는 평면 구조에 적용된 fully depleted silicon-on-insulator 기술에 적용된 SOI층의 두께보다도 더 얇은 수준이다. 이 때문에 소자 동작시 구동전류에 의한 self-heating 효과로 이한 급격한 채널온도증가 및 수반되는 신뢰성 특성 열화등 종래의 bulk 소자에서는 볼 수 없었던 새로운 문제를 우려해야하는 상황이 되고 있다.

뿐만 아니라 7nm급 이후의 세대에서는 <그림 3-3-1-3>에서 볼 수 있는 것과 같이 게이트길이의 미세화에 따라 swing 이 급격하게 증가하는 단채널효과가 다시 발생하고 있다. 이 문제를 해결하기 위해 새로운 소자구조가 필요해지고 있으며, 이와 동시에 각 기술노드별 기술개선효과 감소로 인한 비용대비 효율성 감소문제에 대처할 수 있도록 획기적인 성능을 개선하기 위한 방법 또한 함께 도입되어야하는 상황이다.

시스템반도체 설계 전문가 부족·중견 팹리스 육성 미흡

정부, 차세대소재 R&D투자·지능형반도체 등 개발 지원

현재 가장 우선적으로 고려되고 있는 소자구조는 게이트제어효과를 극대화할 수 있는 gate all around (GAA) 형 소자이다. 일종의 나노와이어소자라고 할 수 있는 이 소자는 평면형과 수직형으로 나뉠 수 있는 데, <그림 3-3-1-4>에 보인 것과 같이 소자특성 제어를 위해 필요한 junction profile 개선이 좀 더 용이한 평면형 소자가 우선적으로 고려되고 있다. 수직형은 집적도 향상에 장점이 있다고는 하나, 미세한 junction profile 구조제어에 적합하지 않다는 한계가 있다. <그림 3-3-1-4(a)>는 나노와이어구조에서 전류가 흐를 수 있는 단면적이 감소되는 문제를 해결하기 위해 여러 개의 나노와이어를 적층하는 방식을 보여주고 있고, <그림 3-3-1-4(b)>는 나노와이어구조에서 구동전류대비 기생 게이트정전용량이 너무 빨리 증가하는 문제를 저감하기 위해 채널단면적을 늘리는 방식으로 나노 sheet 형 채널구조를 사용할 수 있다는 아이디어를 보여주고 있다. 두 구조 모두 단채널효과는 제어가 가능하지만, 채널소재와의 접촉저항이 급격히 증가하는 구조이기 때문에, 실제 소자에서 성능개선효과는 입증되지 않은 상태이다.

위에 언급한 바와 같이 단채널효과를 제어하더라도 소자미세화에 의한 ballistic transport 효과, strain engineering 효과 감소 등의 문제로 인한 소자성능열화문제, swing의 최소값(60mV/sec) 때문에 낮은 전압에서 소자를 동작할 수 없게 되는 저전압동작의 한계 등의 문제가 남아 있어서, 또 다른 수준의 성능개선 대책이 필요하다.

이에 대한 대안으로 채널전하이동도가 높은 InGaAs와 같은 화합물 반도체 소재를 적용하는 III-V MOSFET이 오랫동안 연구되어왔으나, 당초 평면소자용으로 연구되어왔던 기술적 요구사항에 fin 구조형성, 나노와이어 구조형성 등 새로운 기술적 난제들이 추가되면서 아직 주목할 만한 기술적 돌파구가 보고되지 않은 상태이다.

Swing을 개선하기 위한 또 다른 접근방법으로, source에서의 전하주입방식을 바꾸어 줌으로써 60mV/sec swing 한계를 돌파하여. 소자가 더 낮은 전압에서 on상태에 도달할 수 있게 하는 방범으로 동작전압을 낮추고, 소모전력을 저감하거나 성능을 개선하는 기술이 연구되고 있다. 전하주입방식을 바꾸기 위해 기존 MOSFET의 전하확산메커니즘이 아닌 impact ionization에 의한 고에너지 전하주입방식, 고이동도를 갖는 화합물반도체를 source 영역에 형성하는 이종접합방식 등이 있으며, 좀 더 잘 알려진 방법은 source와 drain을 각각 n+, p+ 접합으로 형성하는 asymmetric 접합을 이용하는 tunnel FET(tFET)소자가 있다. iFET과 tFET의 접합구조는 같은 형태이지만, source에서 전하를 가속해서 주입을 하는 지 아닌 지가 주된 차이점이다. tFET의 경우에는 source쪽에서는 tunneling 장벽을 넘어서 전하가 주입될 수 있는 조건이 되면 바로 전류가 흐르기 시작하기 때문에 소자가 켜지는 속도, 즉 swing을 개선할 수 있지만, tunneling 장벽을 넘는 과정이 일종의 저항으로 작용하기 때문에 <그림 3-3-1-6(c)>에 보인 것과 같이 점선으로 표시된 평면 MOSFET 대비 구동전류가 크게 감소하게 된다.

이 문제를 해결하기 위해, <그림 3-3-1-6(a)>에 보인 것과 같이 drain 대비 source의 면적을 늘리는 방법, source에 이종접합을 활용하여 전하주입량을 늘리는 방법 등 다양한 해결방법이 연구되고 있고, 기존 소자의 구동전류대비 대략 1/10 수준까지 개선된 결과도 보고되고 있지만 아직 획기적인 돌파구는 없는 상황이다. 이 때문에 기존 소자의 성능을 매칭하기보다는 <그림 3-3-1-6(c)>에 보인 것과 같이 동작전압이 0.35V이하로 감소되면, 실리콘 MOSFET 의 구동전류보다 tFET의 구동전류가 높아질 수 있는 상황이 되므로 tFET의 도입시기를 VDD=0.4V정도의 기술세대로 설정해야한다는 의견도 있다.

지금까지 주요 소자기술의 문제점들과 해결을 위한 접근방법들에 대해 간략히 요약했는데, 모든 소자들이 공통적으로 안고 있고, 가장 치명적인 문제인 접촉저항의 문제를 간과할 수는 없다. 소자가 미세화되면서 접촉저항에서 IR 전압강하에 의해 손실되는 전압 때문에 실제 소자에 인가되는 전압이 감소되고, 그에 따라 구동전류가 감소되는 문제가 점점 심각해지고 있다. 실리콘 기반소자들의 접촉저항은 기본적으로 금속과 반도체 접촉시 발생되는 쇼트키 접합장벽에서 발생되는 매우 근본적인 현상에서 발생한다는 데 문제해결의 어려움이 있다. 이 문제를 해결하기 위해, source/drain 영역의 도핑농도를 극단적으로 높이는 방법으로 supersaturated doping, laser anneal 등 다양한 공정이 지난 수십 년간 개발되어왔다. 쇼트키 접합장벽을 줄이고 저항이 낮은 Ohmic 접합을 만들기 위해서는 실리콘의 conduction band, valence band와 일함수가 가까운 두 가지의 금속소재를 접합소재로 사용해야한다. 이 때문에 midgap 일함수를 갖고 있는 NiSi에 Er, Pt 등 일함수가 낮은, 또는 높은 금속을 합금하여 쇼트키 접합장벽을 줄이기 위한 연구가 활발히 진행되고 있다. 또 다른 접근방법으로 금속과 반도체 계면에서 발생하는 페르미 레벨 고착 현상을 해결하기 위해 금속과 반도체 계면에 매우 얇은 절연체, 그래핀, 이차원 소재를 삽입하는 연구 등이 진행되고 있는 데, 최근에는 Sn 합금 등을 사용하여 sub-nano ohm/cm2급의 접촉저항개선 방법이 보고되고 있다.

tFET의 경우는 실리콘 소자용으로 개발된 접촉저항개선 방법을 적용할 수 있으나, source/drain에 strain engineering을 위해 SiGe 을 사용하거나, 전하주입속도개선 또는 불연속 밴드구조 형성을 위해 화합물반도체를 사용하는 경우에는 위에 언급된 새로운 접촉저항개선 방법에 대한 연구가 매우 미흡한 수준이다. nanoΩ 또는 그 이하의 접촉저항을 달성할 수 없을 경우 차세대 기술에 적용하기 어렵기 때문에, 차세대 소자기술의 경우 접촉저항의 한계가 기술도입여부를 결정하는 핵심요인이 될 것이다.

이 장에서는 최신 반도체 제품에 적용되고 있는 FinFET 소자 및 차세대 소자기술에 대해 간단히 살펴봤는데, 소자구조 형성에 필요한 공정, 게이트절연막, 접촉저항 개선을 위한 소재, 3차원 나노와이어 소자구조 제작에 필요한 집적공정등 매우 다양한 신기술이 함께 개발되어야만 안정적인 소자 제작이 가능하다는 것을 알 수 있었다. 다음 장에서는 소재, 공정, 집적공정별로 최근 기술개발 동향에 대해 살펴보고자 한다.

■ 초고집적 반도체 소재 기술

반도체분야는 신소재 채택측면에서는 매우 보수적인 입장을 견지해왔다. 실리콘, 질소, 산소 그리고 Al, W, Co, Ni, Cu, Ta, Ti 정도의 물질과 Arsenic, Phosphorus등의 dopant등 한정된 원소만을 이용하여 수십 년간 반도체 소자를 작게 만들면서 발생하는 문제들을 해결해 왔다. 최근에는 새로운 소재, 공정들이 속속 적용되고 있고, 신소재를 적용하는 데 필요한 경험이 축적되면서 새로운 소재의 적용주기도 빨라지고 있는 측면도 있기만, 그만큼 기술적 난관을 돌파하기 어려워지고 있어서 절박한 상황에서 충분한 검증없이 적용되고 있다고 생각해볼 수도 있다. 신소재기술의 경우, 반도체 소자에 요구되는 성능을 모두 만족하는 성능을 갖춘 소재를 개발하는 것이 매우 어렵기 때문에, 향후 소자기술의 한계는 아래에 설명하는 소재의 한계에 의해 결정된다고 볼 수 있을 것이다.

1990년대 초반부터 약 20년간 금속배선 부분에 사용되던 SiO2를 저유전절연체로 대체하기 위한 대규모 국제연구가 진행되었으나, 전기적 유전율, 신뢰성 뿐 아니라 열팽창계수 등을 포함한 구조적문제, 방열문제 등의 요구조건을 만족시킬 수 있는 신소재를 찾는 것이 어려웠기 때문에 유전율이 2.2정도인 SiOCH 수준에서 더 이상 개선이 어렵게 되었다.

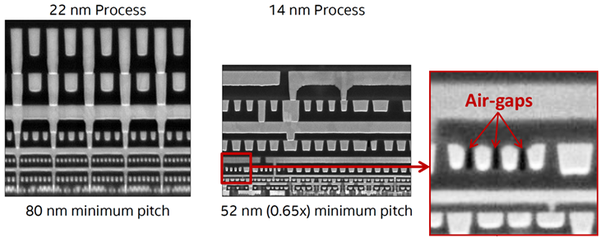

이 때문에 <그림 3-3-1-7>에 보인 것과 같이 유전율 1를 가지는 air gap을 배선 구조내에 형성하여 유효유전율을 낮추는 방향으로 전략을 바꿔, 소재보다는 집적공정을 개선하는 방향으로 연구가 진행되고 있다. 하지만, 이 방법은 배선기술의 미세화를 제한하는 요인이 되고 있다. 최근에는 소모전력의 대부분이 배선부분의 정전용량에 비례하여 발생하기 때문에, 소자의 소모전력을 최소화하기위해서는 공기와 유사한 유전율을 가지면서도 실리콘 산화막과 유사한 구조적 강도를 갖는 소재를 개발할 필요가 있다.

또 다른 사례로 2000년대 초반 90nm급 기술에서부터는 금속배선간의 절연막뿐만 아니라 배선금속을 Al (2.67μΩ-cm) 에서 Cu(1.67μΩ-cm)로 바꾸게 되었다. Cu는 실리콘 내에서의 확산속도가 매우 높고, midgap 결함을 만들기 때문에 대표적인 기피대상 소재였지만, electron migration문제에 대한 내성이 좋고, Al 대비 전도도가 훨씬 높아서, Cu 배선소재가 실리콘 기판으로 확산하지 않도록 하는 barrier소재 TiN, TaN 등과 함께 채택되었다. 그러나 Cu 배선기술도 소자의 미세화가 계속되면서 저항의 한계에 도달하여 단결정구조를 이용하여 저항을 더 낮추거나, barrier 소재의 두께를 줄여서 유효 Cu 배선의 두께를 늘리는 등 최적화 연구가 계속 되고 있지만, 역시 소자의 요구사항을 만족하지 못하는 수준에서 개발이 정체되고 있다. 그래핀 나노리본 또는 Graphite/Cu 적층소재 등 대체소재에 대한 연구도 진행되고 있지만, 아직 기술성숙도는 충분하지 않는 수준이어서 기술혁신이 시급한 분야이다.

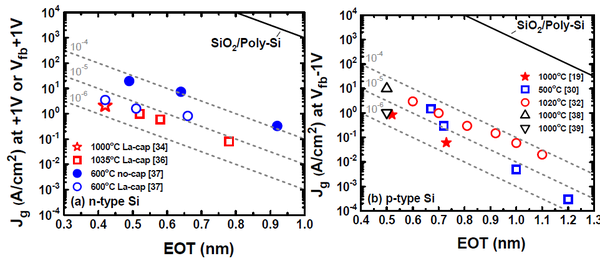

2007년 인텔을 필두로 반도체소자에 Hafnium기반 고유전절연막이 추가되고 TiN, TaAlN등 금속전극이 적용되기 시작했다. 금속전극은 TaN, TiN기반에 Al, Si doping을 통해 유효일함수를 조절하고 있으며, 금속의 grain boundary 제어를 통해 일함수를 균일하게 하는 등의 연구는 진행되고 있으나, 게이트스택부분에서는 기존 Hafnium 기반 고유전절연막의 두께를 줄이는 방법으로 미세화가 진행되고 있고, <그림3-3-1-8>에 보인 것과 같이 다양한 방법으로 미세화가 가능한 상황이어서 새로운 소재에 대한 수요는 많지 않다. 고유전절연막의 경우 결정구조 제어를 통해 유전율을 ∼20에서 ∼40까지 높이는 것이 가능하다는 사례가 보고되고 있으나 기술성숙도는 낮은 편이다.

Silicon 채널소재를 대체하기 위한 노력은 40년 이상 계속되어 왔고, 2000년대 초반부터는 Ge 또는 GaAs기반 화합물반도체를 사용하기 위한 연구가 본격화되었다. Ge은 1960년대에 bandgap이 작고, 열적안정성이 좋지 않아서 폐기되었던 기술인데, 소자동작전압이 낮아짐에 따라 다시 활용가능성이 검토되고 있고, strain engineering을 위해 source/drain에 SiGe 이 이미 도입되어있어서 진입장벽은 높지 않은 수준이다. 화합물반도체는 소자이동도가 매우 높아서 사용가능성에 대한 연구가 1970년대부터 꾸준히 진행되어왔고, HEMT소자 등 특수분야에 적용되는 기술도 개발되었으나, MOSFET구조에 꼭 필요한 게이트 절연막을 개발하지 못하는 것이 문제였다.

최근 ALD기반의 고유전절연막 증착기술이 채용되면서 게이트 절연막 형성 문제를 극복할 수 있을 것으로 생각했으나, 아직 contact 저항 문제 등 근본적인 문제가 해결되지 않아 전면적인 적용이 지연되고 있다. 인텔은 22nm급 소자에서부터 적용가능성을 시사해왔으나, 7nm급 소자에서도 아직 채용되지 않고 있으며, 향후 gate all around (GAA)소자가 적용될 것으로 예상되고 있는 5nm급 이후에는 SiGe 희생층과의 선택적 epi 및 식각공정이 어려워서 insertion point를 놓치고 있는 것으로 보여진다.

<그림 3-3-1-9>는 다양한 소자구조에서 III-V 소자를 만들었을 경우, Interface와 contact 저항이 최상의 수준에 도달할 수 있으리라는 가정하에 소자의 성능을 시뮬레이션한 결과이다. GAA소자구조에서 가장 높은 동작속도를 얻을 수 이었지만, roadmap target을 만족하지는 못했다. <그림 3-3-1-10>은 좀 더 비관적인 결과를 보여준다. 이론적으로 SiGe을 사용할 경우, 나노Ω급의 접촉저항을 달성할 수 있으나, InGaAs 의 경우 <그림 3-3-1-6(b)>에 보인 것과 같이 이론적인 연구로도 10나노옴 이하로 접촉저항을 줄이는 것이 어려울 것으로 예측되고 있다.

차세대 반도체 기술의 개발성과는 위에 언급한 것과 같이 배선절연막, 배선소재, 접촉저항소재 등의 개발성과에 의해 결정될 것으로 생각되어 그 중요성은 아무리 강조해도 지나치지 않을 것이다.

▲ <그림 3-3-1-1>32nm급 소자와 22nm급 소자구조의 변화

▲ <그림 3-3-1-1>32nm급 소자와 22nm급 소자구조의 변화 ▲ <그림 3-3-1-2>14nm 급 소자의 단면구조 및 주요 dimension parameters

▲ <그림 3-3-1-2>14nm 급 소자의 단면구조 및 주요 dimension parameters ▲ <그림 3-3-1-3>fin의 두께에 따른 소자 특성 개선 추세

▲ <그림 3-3-1-3>fin의 두께에 따른 소자 특성 개선 추세 ▲ <그림 3-3-1-7>인텔의 BEOL 배선 구조(2014)

▲ <그림 3-3-1-7>인텔의 BEOL 배선 구조(2014) ▲ <그림 3-3-1-8>La2O3 capping층의 oxygen 흡수효과를 이용한 HfO2 절연막의 scaling 한계

▲ <그림 3-3-1-8>La2O3 capping층의 oxygen 흡수효과를 이용한 HfO2 절연막의 scaling 한계 ▲ <그림 3-3-1-9>다양한 소자구조에서 III-V MOSFET 모델링 결과

▲ <그림 3-3-1-9>다양한 소자구조에서 III-V MOSFET 모델링 결과