차세대 반도체 소재, 시냅스·다진법 반도체 주목

선폭 1nm 이하 한계, 실리콘 대체·패러다임 극복 必

시냅스 소자, CMOS 공정 호환성·유전체 소재 선택 중요

1. 기술의 개요

1.3 기술의 중요성

현재 반도체의 선폭은 양산 기준으로 3nm가 최소이며, 1.4nm가 개발되고 있다. 현재의 실리콘 기반 반도체의 고집적도 한계를 극복하고자 EUV의 노광 기술이 개발되고 이에 맞추어 주요 공정 기술이 함께 개발됐다.

하지만 1nm 이하가 되면 물리적인 한계에 도달하게 돼 극한 환경이 될 것이며, 이를 극복하려면 실리콘을 대체하면서도 현재의 패러다임을 극복한 새로운 기술이 제시돼야 한다. 이의 대표적인 기술이 앞서 소개한 시냅스 소자와 다진법 소자이다.

하지만 소재 측면에서 실리콘의 표준화된 공정 수준으로 선폭을 줄이고 양산성과 내구성을 확보하려면 시냅스 소자와 다진법 소자가 요구하는 특수한 특성뿐 아니라 기존의 CMOS 공정 호환성, 내열내습성, 동작 안정성 등을 모두 갖추어야 한다. 먼저 시냅스 소자의 경우에는 2단자의 멤리스터 방식 소자가 주로 연구돼 왔으나 현재는 다양한 방식의 3단자 소자의 연구가 발표되고 있다.

기존의 황화물이나 셀레늄 화합물과 같은 이차원 반도체의 경우에는 대면적의 양산성 확보가 요구되며, 초미세 선폭과 같은 극한 환경에 적용되기에는 반도체 공정 호환성이 아직 미흡한 실정이다. 또 유기 반도체의 경우 내구성이나 대면적 제조 및 CMOS 공정 호환성 확보가 숙제로 남아 있다.

최근에는 CMOS 공정 호환성을 갖춘 도핑된 하프늄산화막(HfO2) 혹은 HfZrO와 같은 화합물이 특정 성장 조건에서 강유전성을 나타내는 특성을 보여 이를 활용해 시냅스 소자를 구현하는 보고가 있었고, 후속 연구도 활발히 진행되고 있다. 다만, 이 물질의 경우에는 동작 안정성과 시냅스 특성의 향상이 중요하다.

다진법 소자의 경우는 반도체의 pn 접합을 통해 터널링 동작으로 음미분 저항을 형성시켜야 하는데, 기존의 실리콘을 대체하면서도 pn 접합을 형성해야 한다. 기본적으로 이 경우도 작은 선폭을 형성하려면 반도체 공정에 호환되는 소재를 선택해야 한다.

대면적 양산성을 위해서는 진공 증착법으로 제조할 수 있으며, 노광과 식각 공정을 비롯한 주요 공정을 적용할 수 있어야 한다. 또 트랜지스터에서는 반도체와 절연막의 소재 내구성이 확보돼야 하며, 내열내습성도 갖추어야 한다.

현재 다양한 소재가 채택돼 연구되고 있으나 이차원 반도체와 유기 반도체의 경우에는 이러한 CMOS 공정 호환성이나 내구성을 확보하는 데 어려움이 있으므로 이를 타개할 만한 소재를 선택하는 것이 중요하다.

2. 시냅스 반도체와 다진법 반도체의 연구개발 동향

2.1 시냅스 반도체 연구 동향

시냅스 소자는 뉴런과 뉴런의 연결 부분인 시냅스를 모사하는데, 전기 자극에 대해 전류의 가중치가 필요하므로 가변 저항이 기억되는 형태의 소자가 요구된다.

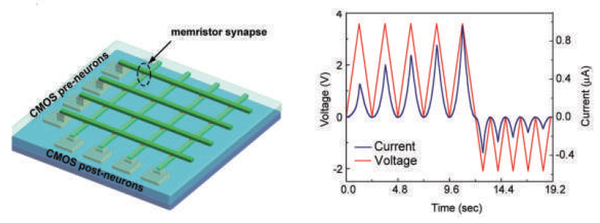

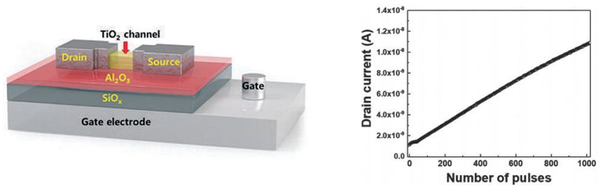

▲ <그림 1>멤리스터 방식의 소자 연결 부분(左)과 전압 펄스 인가에 대한 전류의 증폭 과정(右)

▲ <그림 1>멤리스터 방식의 소자 연결 부분(左)과 전압 펄스 인가에 대한 전류의 증폭 과정(右)기존의 메모리 연구로 수행됐던 멤리스터는 가변저항이 시냅스의 가중치로 인식돼, 반복되는 자극에 따라 학습돼 전류가 변화하는 양상을 보여 주므로 시냅스 특성을 모사하는데 적합하다.

<그림 1>은 전형적인 멤리스터 소자의 어레이 구조를 보여 준다. 우측은 양의 전압 펄스가 반복됨에 따라 전류의 값이 점차로 증가하는 강화 학습을 보여 주고, 반대로 음의 전압 펄스가 반복되면서 전류 값이 점차 감소하는 억제 학습을 보여 준다.

시냅스 반도체는 연구 동향이 크게 2단자 소자와 3단자 소자로 분류되는데, 가장 대표적인 2단자 소자는 저항 메모리(RRAM)와 상변이 메모리(PCM)이다. 저항 메모리는 비교적 간단한 MIM(금속-절연체-금속) 구조이며, 절연체에서 전도성 필라멘트가 생성됐다가 없어지기도 하는 구조이다.

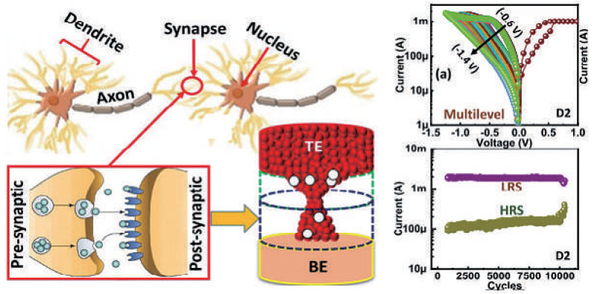

▲ <그림 2>멤리스터 방식의 소자 연결 부분(左)과 전압 펄스 인가에 대한 전류의 증폭 과정(右)

▲ <그림 2>멤리스터 방식의 소자 연결 부분(左)과 전압 펄스 인가에 대한 전류의 증폭 과정(右)전도성 필라멘트는 <그림 2>와 같이 전극과 전극 사이의 절연체에서 형성된다. 이러한 전도성 채널은 전압 자극에 따라 점차 전도도가 증가하거나 감소하는데, 저저항 상태인 LRS와 고저항 상태인 HRS를 형성하며 많은 반복 동작인 사이클 수에 따라서 전류 값을 일정하게 유지하는 동작 안정성이 매우 중요하다.

전도성 채널에서 금속 이온이 형성되는 경우 컨덕티브 브리징 램(conductive bridging RAM, CBRAM)으로 불리는데, 예시로 Cu, HfO2, Pt나 Ag, GeS2, W 등의 구조가 있다. CBRAM 소재에서는 금속 전극의 양이온이 전도성 채널을 형성해야 하므로 전극 소재 선택이 중요하다. 이 소자의 장점은 빠른 스위칭 속도와 저전력이지만, 확률적으로 각 상태가 일정하지 않아 양산 적용 시 장벽이 되고 학습 시 비선형적으로 증가하는 양상을 보여 준다.

또 다른 RRAM의 형태는 filamentary RAM으로서 같은 MIM구조이지만, 금속 이온이 아닌 산소 공공(vacancy)이 전도성 필라멘트를 형성한다. 이 경우 전기장에 따라 저저항과 고저항 상태가 구현되며, 주로 사용되는 절연막의 소재는 TiOX, HfOX, AlOX, WOX, TaOX 등의 산화물이다.

이 소자는 전기장에 따라 소프트 브레이크다운(soft breakdown)이 발생하고, 산소 이온과 공공의 분리와 재결합에 따라 전도성 필라멘트가 형성되는 시냅스 특성이 나타난다. CMOS 호환성을 갖추고 있으며, 비용이 저렴하고, 프로그램 속도도 10~100ns로 비교적 빠른 편이어서 장점이 많지만, 대면적 균일성과 비선형적 학습 곡선 및 확률적인 불안정성으로 개선의 여지가 많다.

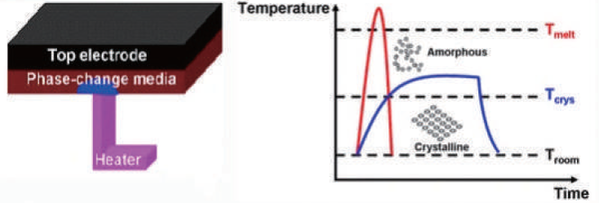

또 다른 2단자 시냅스 소자의 대표적인 형태는 상변이 메모리이다. 결정상과 비정질상 전기저항의 차이를 이용해 급격한 저항 변화를 통해 시냅스 특성을 구현하는 소자이다. 기본적인 구조는 <그림 3>과 같이 상하부 전극(2단자) 사이에 상변이 물질과 히터가 존재하고, 전기를 가해 주면 국부적인 열이 발생해 온도 변화로 비정질에서 저저항의 결정상이 형성되는 특성을 활용한다.

<그림 3>의 우측처럼 결정 온도 이상에서는 결정상이 돼 저저항 상태로 바뀌는데, 열을 더 가해 주어 용융점(melting point) 이상이 되면, 다시 비정질로 바뀌어 고저항 상태가 된다. 이와 같은 설정(set)과 재설정(reset) 과정을 통해서 저저항과 고저항 상태 사이에 많은 전도상태를 구현해 시냅스 특성을 나타낸다.

▲ <그림 3>상변이 메모리 소자의 구조(左) 및 온도 변화에 따른 상의 변화(右)

▲ <그림 3>상변이 메모리 소자의 구조(左) 및 온도 변화에 따른 상의 변화(右)상변이 메모리 시냅스 소자의 장점은 빠른 속도와 간단한 구조이지만, 대면적 균일도 형성이 어렵고, 학습 정확도가 떨어지며, 결정화도 확률적인 불안전성에서 벗어나지 못한다는 단점이 있다.

이와 같이 2단자 시냅스 소자는 단순한 구조와 비교적 빠른 스위칭 속도 및 저전력으로 우수한 장점이 많으나, 대면적으로 양산 공정을 수행하기에 아직은 개선 여지가 많고, 전송과 학습이 동시에 이루어지며, 멀티 터미널의 연산을 필요로 할 때 대응하기 어렵다는 단점을 가지고 있다. 이를 위해 최근에는 3단자의 시냅스 소자도 다양하게 연구하고 있다.

3단자 시냅스 소자는 다양한 방식으로 다양한 소재를 적용해 연구되고 있는데, 기본적으로 소스, 드레인과 게이트의 전극을 포함하는 트랜지스터 형태의 구조를 갖추었다. 대표적으로 강유전체 방식, 전해질 방식, 계면 전하 트랩 방식이 있다.

먼저, 강유전체 방식은 잔류 분극을 이용하는 방식이며, 강유전체를 게이트 유전막으로 채용해 전압 펄스를 인가한 후 전압이 제거돼도 분극이 남아 있어서 채널의 전류에 영향을 준다. 기존에 잘 알려진 PZT, BST등의 강유전체는 CMOS 공정의 호환성 확보가 어렵고 내구성이 만족스럽지 못했으나 최근에 HfO2와 ZrO2의 화합물 박막에서 강유전성이 보고돼 CMOS 호환성을 확보할 수 있게 됐다.

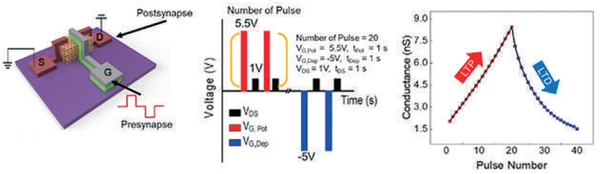

▲ <그림 4>HfOX 강유전체 박막을 활용한 시냅스 트랜지스터 구조(左) 및 인가 전압 펄스의 변화에 따른 강화 학습과 억제 학습 경향(右)

▲ <그림 4>HfOX 강유전체 박막을 활용한 시냅스 트랜지스터 구조(左) 및 인가 전압 펄스의 변화에 따른 강화 학습과 억제 학습 경향(右)이후에 다양한 반도체의 3단자 소자에 HfO2 계열의 강유전 박막이 적용됐는데, 최근에는 HfO2 박막에 ALD 방법으로 Si, Al 등을 도핑한 경우에도 강유전성이 보고돼 시냅스 소자로 활용되는 결과도 보고됐다.

<그림 4>는 HfO2에 Al을 도핑해 강유전성을 얻은 박막을 게이트 유전막으로 활용하고, ICZO(InGaZnO 화합물) 박막을 반도체로 사용한 시냅스 반도체의 구조와 학습 특성을 보여 준다.

이 경우, 강유전성에 따라 시냅스 특성이 성공적으로 얻어졌으나, 분극의 경우에는 LTP의 특성 구현은 잘되지만 오히려 STP의 구현으로 학습할 경우, 바로 LTP로 도달해 학습 상태 수를 많이 확보하지 못하고 선형적인 증가를 얻지 못한다는 단점이 있다.

<그림 4>와 같이 일정한 전압 크기의 양의 펄스가 공급됐을 때, 전도도가 증가하다가 바로 포화되는 경향을 보여 선형성이 떨어지고, 구현하는 상태 수가 많지 않은 것을 알 수 있는데, 이를 극복하려면 전압의 크기를 점차 증가하는 방식으로 선형성을 개선할 수 있음도 확인할 수 있다.

하지만 실제 시냅스 소자로 활용되는 경우에는 전압 크기를 변조하는 방식은 바람직하지 않기 때문에 이러한 단점을 보완하도록 소재 차원에서 더 근본적인 아이디어가 필요해 보인다.

3단자 시냅스 소자로 활용되는 전해질 방식은 3단자 소자에서 게이트 유전막에 해당하는 곳에 전해질 소재를 적용하여 이온이 인가 전압에 따라 전해질 내부를 이동하는 방식을 활용한다. 전해질은 통상 액체가 사용되지만, 시냅스 소자의 경우 반도체 공정 호환성이나 생산 측면에서는 고체 전해질을 선호하며, 고체 전해질을 적용하여 시냅스 특성을 구현하는 연구가 진행돼 왔다.

▲ <그림 5>Li silicate 고체 전해질을 활용한 시냅스 소자의 구조(左) 및 전압 펄스 형태와 강화 및 억제 학습의 모습(右)

▲ <그림 5>Li silicate 고체 전해질을 활용한 시냅스 소자의 구조(左) 및 전압 펄스 형태와 강화 및 억제 학습의 모습(右)이러한 전해질 소재의 게이트 유전막에서는 통상적으로 양이온이 위치하며, 게이트 전압에 따라서 전해질 내에서 이동하면서 채널에 흐르는 전류의 양을 제어할 수 있게 된다. <그림 5>는 그 한 예로 MoS2 이차원 반도체를 반도체 채널로 사용하고, Li 이온을 Li 화합물의 전해질 내에서 이동시켜 시냅스 특성을 구현한 소자의 구조와 동작을 보여 준다.

이때 양이온은 게이트 양의 전압에 대하여 전해질과 채널의 경계 쪽으로 이동하여 채널에 있는 전자를 유도하여 전도도를 증가시키는데, 채널로 침투하지 않은 상태에서는 전기이중층(Electric double layer, EDL)을 형성시키게 된다.

만일 인가 전압의 크기가 더 크게 증가하면 이온들은 채널로 침투하는데, 이 경우에는 전도도가 더 증가하는 양상으로 나타나고, 이 경우를 일렉트로우케미컬 도핑(electrochemical doping)이라고 한다.

고체 전해질의 경우에는 on/off 전류비가 아주 크지 않아서 구현할 수 있는 상태 수가 많지 않다는 점과 전해질과 반도체 소재에서 선택의 폭이 크지 않다는 단점이 있지만, 향후 이러한 단점을 잘 보완하는 소재가 발굴된다면 우수한 시냅스 특성도 기대해 볼 수 있다.

3단자 소자의 3번째 방식은 계면 전하 트랩 방식이며, 반도체와 게이트 유전막의 계면에 존재하는 트랩에 의하여 전자나 정공의 포획/방출을 통해 시냅스 특성을 달성하는 것이다. 이러한 방식에서 중요한 것은 반도체와 유전막의 소재 선택과 제조 공정이다.

통상적으로 반도체나 유전체 소재에서 트랩은 결함을 의미하며, 이러한 결함 때문에 트랜지스터의 이동도가 감소하고, 내구성이나 동작 안정성이 저하되는 특성을 나타내어 최소화하는 방향으로 소자가 제조된다.

하지만 계면에서의 트랩은 에너지 밴드갭 내에서 전도대역 근처에 있는 쉘로우 트랩(shallow trap)과 밴드갭 내에 깊숙이 있는 딥 트랩(deep trap)으로 분류할 수 있으며, 쉘로우 트랩에 포획된 전하들은 포획과 방출이 쉬워서 동작 안정성이 저하되지만, 딥 트랩에 포획된 전하들은 오히려 우수한 내구성을 보인다. 따라서 계면의 트랩을 선별적으로 남겨 놓으면 트랩에 포획된 전하의 수에 따라 더 넓은 범위의 전도도와 우수한 선형성을 확보할 수 있게 된다.

▲ <그림 6>산화물 반도체와 절연막 계면의 트랩을 활용한 3단자 시냅스 소자의 구조(左) 및 우수한 선형성을 보이는 강화 학습의 모습(右)

▲ <그림 6>산화물 반도체와 절연막 계면의 트랩을 활용한 3단자 시냅스 소자의 구조(左) 및 우수한 선형성을 보이는 강화 학습의 모습(右)시냅스 소자에서는 향후 양산을 위하여 CMOS 공정 호환성이 매우 중요하므로, 반도체와 유전체의 소재를 선택하는 것이 매우 중요하다. 계면 트랩 전하 방식의 몇 가지 사례로 이차원 반도체와 산화물 반도체가 주로 연구되었는데, 이차원 반도체의 경우에는 아직 공정 호환성을 갖추지 못했고, ZnO(IGZO 포함)나 TiO2와 같은 산화물 반도체는 반도체 공정을 활용할 수 있고 우수한 내구성을 갖추었다는 점에서 양산에 더 가까운 소재라고 할 수 있다.

<그림 6>은 산화물 반도체와 이중층의 유전박막을 활용하여 제조한 시냅스 트랜지스터 소자로서 계면의 trap에서 전하를 포획하고 방출하면서 강화와 억제 학습을 나타낸다. 특히 이 소자는 전기 신호뿐 아니라 광 신호에도 시냅스 특성을 보이는 특징을 지녔는데, <그림 6>의 오른쪽처럼 1,024개의 전도 상태에서 매우 우수한 선형성을 보이는 광 시냅스 특성을 지녔다.

이와 같이 현재 고집적 반도체로 활용되는 시냅스 소자는 다양한 방법으로 연구가 진행되고 있으며, 머지않아 CMOS 공정 호환성과 우수한 내구성을 갖춘 인공지능 소자가 개발될 것이다. 특히 연산과 기억을 동시에 하는 로직 인 메모리 소자도 개발될 것이다.