2세대 AI반도체 성공, 新소재 관건

■ 2세대 인공지능 반도체

1) 국내 동향

생물학적 신경망과 유사한 집적도를 갖는 2세대 인공지능 반도체를 위해서는 생물학적 시냅스의 핵심 특성을 모두 갖는 인공 시냅스를 하나의 소자로 구현해야 한다. 이러한 목적을 달성하기 위하여 다양한 인공 시냅스 소자가 제안되고 제작되어 왔다. 이들 대부분의 소자는 플래시 메모리(flash memory), RRAM(resistive random access memory), PRAM(phase-change random access memory), MRAM(magnetic random access memory) 등의 메모리 셀(cell)에 기반한 것이다. 집적도를 높이기 위해서 소자의 크기가 작아야 하고, 하나의 시냅스가 여러 가지 가중치를 갖도록 점진적인(gradual) 스위칭(switching) 특성이 중요하다.

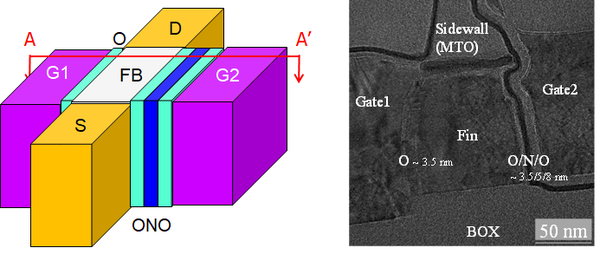

국내의 플래시 메모리 기반 시냅스 소자 연구는 서울대를 중심으로 이루어지고 있다. 그림 10은 플래시 메모리에 기반한 플로팅 바디 시냅스 소자(floating-body synaptic transistor, FST)이다.

이 소자는 2개의 독립적인 게이트 G1과 G2를 가지고 있다. G1은 채널(channel)의 반전층(inversion layer)을 형성하고 조절하며, G2는 채널의 반송자(carrier)를 전하트랩 층(질화막)으로 옮기는데 사용된다. 두 게이트 사이의 플로팅 바디는 채널로 사용되며, 동시에 충격이온화(impact ionization)나 게이트 유도 드레인 강하(gate-induced drain lowering)에 의해 생성된 과잉 반송자의 저장 장소로도 활용된다. 플로팅 바디에 저장된 과잉 반송자(excess carrier)의 문턱전압(threshold voltage) 강하 효과는 단기 기억 메커니즘으로 활용된다. 스파이크 사이의 시간 간격이 짧으면 과잉 반송자가 플로팅 바디에 축적되고, 양의 귀환(feedback) 효과가 바디 전압을 급속히 증가시킨다. 바디 전압이 충분히 증가하여 G2 부근에서 고온 반송자(hot carrier)를 생성하게 되면, 이 고온 반송자가 질화막으로 주입되고, 단기 기억에서 장기 기억으로의 전환(transition)이 일어나게 된다. 스파이크 사이의 시간이 길어지면, 플로팅 바디 내의 과잉 반송자가 재결합(recombination)하게 되고, 단기 기억에서 장기 기억으로의 전환은 일어나지 않는다.

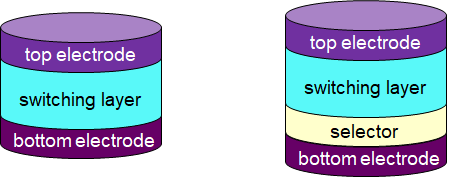

RRAM 기반의 시냅스 소자는 그림 13에서와 같이 구조가 매우 간단하며, 집적도가 높다는 장점이 있다. RRAM은 상부 전극(top electrode)과 하부 전극(bottom electrode) 사이에, 인가하는 전압의 크기와 방향에 따라 저항값이 변할 수 있는 스위칭 층(switching layer)을 삽입한 형태이며, 저항값의 변화에 의해 정보를 저장하는 기억장치(memory)이다. 여러 개의 RRAM 셀(cell)을 병렬로 연결할 경우 의도하지 않은 전류 통로가 형성될 수 있으므로, 이를 방지하기 위해 그림 13(b)에서와 같이 선택소자(selector)를 포함하기도 한다.

포항공대에서는 산화 하프늄(HfO2), 산화 티타늄(TiO2) 등의 다양한 스위칭 물질(switching material)을 사용하여, 여러 단계(level)의 저항값 구현이 가능하고 대칭적인 저항변화 특성을 갖는 시냅스 제작을 위한 연구를 진행하고 있으며, 서울대에서는 질화규소(Si3N4)를 스위칭 물질로 사용하여 점진적 스위칭 특성과 선형적인 저항 변화를 갖는 시냅스 제작을 위한 연구를 하고 있다.

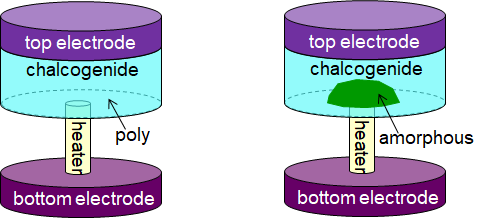

PRAM을 사용한 시냅스 소자의 구조가 아래 그림에 나와 있다. PRAM은 칼코게나이드(chalcogenide)가 열에 의해 상변화(phase change)를 일으키는 특성을 이용하여 메모리 셀의 저항을 변화시키는 비휘발성(non-volatile) 메모리이다. 아래 그림 (a)는 낮은 저항 상태로 칼코게나이드 물질 전체가 다결정(poly-crystal) 상태여서 큰 전류를 흘릴 수 있고, 아래 그림 (b)는 높은 저항 상태로 히터(heater) 근처의 칼코게나이드 물질이 비정질(amorphous) 상태여서 작은 전류가 흐르게 된다. 낮은 저항 상태에서 높은 저항 상태로 변화시키기 위해서는 높은 전압에서 짧은 시간의 전압 펄스를 가하여 비정질화 시키게 되는데, 펄스의 수를 증가시킴에 따라 점진적인 저항의 증가(가중치 약화(depression))를 얻을 수 있다. 반대로 높은 저항 상태에서 낮은 저항 상태로 변화시키기 위해서는 낮은 전압에서 긴 시간동안 전압을 가하여 결정화를 시키게 되는데, 이때 결정화가 짧은 시간 구간에서 일어나므로 점진적인 저항의 감소(가중치 강화(potentiation))를 얻기 어렵다.

PRAM 기반 시냅스에서는 가중치 강화와 약화 시에 발생하는 비대칭적 특성 문제를 극복하기 위하여 텔루륨화 게르마늄-구리(germanium copper telluride, GCT)와 같은 새로운 칼코게나이드 물질을 도입하고 사용 펄스 전압의 형태를 개선하는 연구가 한양대에서 진행되었다.

펄스 전압을 높이고, 펄스 지속시간을 짧게 가져감으로써 점진적인 가중치 변화를 얻을 수 있었고, 이러한 펄스 조건에서 적절한 STDP 특성을 구현하였다.

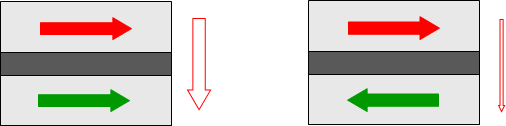

MRAM 기반의 시냅스에서는 그림 15와 같은 자기터널접합(magnetic tunnel junction, MTJ)을 사용한 연구가 진행되고 있다. MTJ는 두 강자성층(ferromagnetic layer) 사이에 얇은 절연막(insulating layer)을 넣은 구조로, 절연막이 매우 얇으면 전자가 한 강자성층에서 다른 강자성층으로 터널링(tunneling)을 통해 이동할 수 있게 되는데, 터널링에 의해 흐르는 전류는 두 강자성층이 같은 방향으로 자화되어 있을 때 크고(아래 그림(a)), 반대 방향으로 자화되어 있을 때 작다(아래 그림(b)). 두 강자성층의 자화 방향을 조절하는 방법으로 최근 도입된 스핀전달토크(spin transfer torque, STT) 방식에서는 전류를 흘려줌으로써 아래쪽 강자성체의 자화 방향을 바꿀 수 있기 때문에 MTJ를 시냅스로 사용하기가 쉽게 되었다. 한양대에서는 CoFeB/MgO/CoFeB 구조를 기반으로 하고 여기에 다양한 물질 층을 추가한 STT-MTJ를 시냅스로 사용하여 조건 반사에서와 같은 연상기억(associative memory)을 구현할 수 있음을 보였다.

지금까지 소개한 인공 시냅스이외에 2세대 인공지능 반도체의 중요한 빌딩 블록으로 인공 뉴런이 있다. 인공 뉴런에서는 시냅스를 통과하면서 가중치가 곱해져서 들어오는 입력신호를 적분(integration)하고, 그 적분된 결과에 따라 적절한 출력을 내놓아야 한다. 출력의 형태는 여러 가지가 될 수 있지만, 여기서는 시간 차원에 대한 고려와 에너지 효율 관점에서 우위에 있는 스파이크 신경망(SNN) 위주로 기술하려 한다.

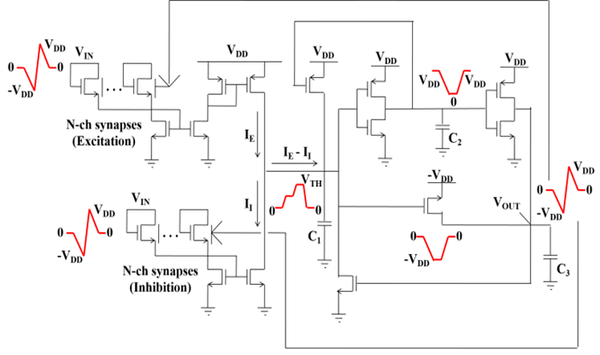

스파이크 신경망은 입력신호를 시공간 적분(spatiotemporal integration)한 결과가 문턱 값을 넘으면 스파이크를 발생한다. 이러한 인공 뉴런은 아래 그림에서와 같이 적분-발화(integrate-and-fire) 회로를 통하여 구현된다.

서울대에서 제안하고 집적회로로 구현한 이 회로는 두 개의 전류 거울을 사용하여 흥분성(excitatory)과 억제성(inhibitory) 시냅스 동작을 구현하고 있으며, 그림 12에 나와 있는 플로팅 바디 시냅스 트랜지스터(FST)를 시냅스로 사용하는 인공 뉴런 회로이다.

스파이크 전압에 의해 형성된 입력 전류는 커패시터 C1에 의해 적분되고, C1의 전압이 다음 단의 문턱전압에 도달하면 스파이크 전압이 발생하며, 장기 기억과 STDP 특성을 구현하기 위하여 시냅스 소자의 제2 게이트(G2)에 이 회로의 출력 전압을 귀환(feedback)시켜 인가한다. 이 과정에서 시냅스 소자가 4단자 소자로서 독립된 2개의 게이트를 가지고 있다는 사실이 큰 장점으로 작용한다.

만약 시냅스 소자가 RRAM이나 PRAM과 같은 2단자 소자라면 시냅스 소자의 한쪽 단자에 직접 연결해야 할 것이고, 그렇게 될 경우 시냅스에 역방향 전류가 흐를 뿐 아니라, 시냅스와 이후 뉴런의 연결을 끊어 주어야 하는 복잡한 문제가 생긴다. 생물학적인 신경망에서는 이 문제를 다양한 생화학적 채널을 사용하여 손쉽게 해결하고 있는데, 이러한 사실로부터 시냅스가 겉보기에는 2단자 소자처럼 보이지만 사실은 여러 단자가 있는 전자 소자에 해당한다는 것을 알 수 있다.

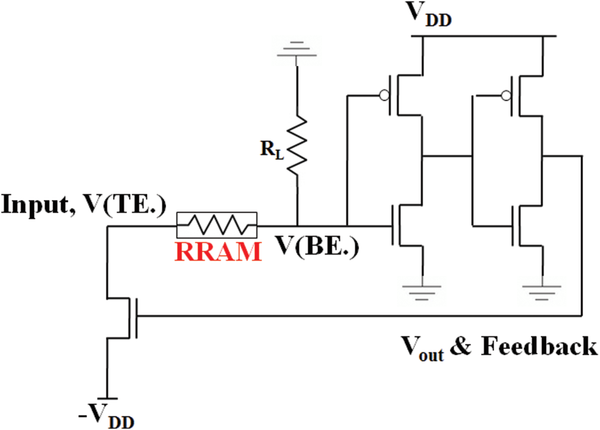

점진적인 저항 변화와 급격한(abrupt) 스위칭 특성을 모두 갖는 RRAM이나 PRAM 등을 활용하여 전력 소모를 줄이고, 소자 수를 감소시켜 인공 뉴런이 차지하는 면적을 줄이는 방법도 연구되고 있다. 아래 그림은 서울대에서 제안한 RRAM을 활용한 적분-발화 뉴런의 회로도이다. 여기에 사용된 RRAM은 Ag/Si3N4/TiN 구조로 만들어졌으며, 특정 전압에 도달하기까지는 점진적인 저항 변화가 일어나다가 특정 전압에 도달하면 급격한 스위칭이 일어나게 된다. 점진적인 저항 변화를 통하여 가중된 입력 신호들의 합을 시간 적분하고, 특정 전압에 도달하면 스위칭을 일으켜 출력에서 스파이크가 발생하도록 하는 것이다.

2) 해외 동향

해외의 2세대 인공지능 반도체에 대한 연구는 미국, 유럽, 중국 등에서 이루어지고 있는데, 대부분 빌딩 블록에 대한 연구 위주로 진행되어 왔지만 최근에 시스템에서의 가능성을 테스트해 보는 방향으로 발전하고 있다. 단일 소자로 인공 시냅스를 구현하는 방법으로 주로 RRAM, PRAM, MRAM 기반의 접근 방법이 시도되고 있으며, 비휘발성 메모리를 뉴런 자체 또는 뉴런 회로의 일부로 사용하는 연구도 활발히 진행되고 있다.

RRAM 기반의 시냅스 연구는 미국 스탠퍼드대(Stanford University)에서 많은 연구가 이루어졌고 이후 타이완 등에서 발전시켜 나가고 있다. 필라멘트(filament) 형 RRAM의 경우 시냅스 강화(RRAM set) 및 약화(RRAM reset) 시 급격한(abrupt) 스위칭이 일어나는 것이 일반적이어서, 점진적인 스위칭을 얻기 위한 다양한 방법들이 제안되었다. 초기에는 시냅스 강화 시 TiN/HfOx/AlOx/Pt 소자에서 점차 증가하는 외부 규제 전류(compliance current)를 사용하고, 약화 시 TiN/Ti/AlOx/TiN RRAM 소자에서 점차 증가하는 리셋(reset) 전압을 사용하여 다단계 스위칭 특성을 구현하였다. 그러나 이와 같이 규제 전류 또는 펄스 전압을 조절하여 저항 변화를 이끌어 내는 방법은 주변회로 설계나 복잡도 관점에서 여러 단점을 가지고 있어, 필라멘트 형 RRAM에서 리셋 동작만을 사용하고 두 개의 RRAM 소자를 이용하여, Pt/HfOx/TiOx//HfOx//TiOx/TiN 다층 산화막 기반 시냅스 소자에서 수백 단계의 저항 상태를 얻는 방법이 제안되었다.

로드맵·장기적 전략 바탕 적극적 기업 참여 必

인공 시냅스·뉴런 구성 소재 연구 중요해질 것

비 필라멘트 형(non-filamentary) RRAM의 경우에는 급격한 스위칭 문제가 적어서 거의 연속적인 시냅스 가중치 형성이 가능하지만, 낮은 에너지 장벽을 요구하는 프로그램 속도와 높은 에너지 장벽을 요구하는 보유시간(retention) 사이에 상충관계(trade-off)가 있다. 미국 미시간(Michigan)대에서는 Pd/WO3/W 구조를 사용하여 점진적인 저항변화를 구현하였으며, 타이완의 교통대(Chiao Tung University)에서는 Ta/TaOx/TiO2/Ti 구조를 사용하여 거의 연속적으로 변하는 특성을 얻었을 뿐 아니라, 생물학적인 시냅스의 스파이크 당 에너지 수준인 7 fJ의 에너지를 사용하는 시냅스 동작을 보였다.

PRAM 기반의 시냅스는 주로 프랑스의 CEA-LETI와 미국의 스탠퍼드대에서 연구되어 왔다. CEA-LETI에서는 GST(GeSeTe)와 GeTe PRAM cell을 제작하고 측정한 데이터로부터 모델을 만들어 동적 비전 센서(dynamic vision sensor)로부터 특징 추출(feature extraction) 모의실험을 하여, 6차선의 고속도로에 있는 자동차의 수를 세는데 성공했다.

이 과정에서 2 개의 PRAM 셀을 묶어 하나의 시냅스로 사용하였으며, 총 200만 개 정도의 시냅스가 사용되었다.

스탠퍼드대에서는 시냅스 당 하나의 PRAM 셀을 사용하여 대칭 및 비대칭 STDP를 구현하였다. 시냅스 가중치 약화를 위해 점차 증가하는 reset 펄스를 사용하고, 강화를 위해 점차 감소하는 set 펄스를 사용하였으며, 에너지 효율을 높이기 위해 짧은 펄스를 사용하였다.

이후 트랜지스터에 의해 선택되는 PRAM 셀을 100×100 배열(array)로 제작하여 배열 수준에서의 학습이 가능함을 실험적으로 보이고, 몇 가지 간단한 패턴에 대해 STDP 학습이 가능함을 입증하였다.

최근 이탈리아의 연구진은 1T1R (트랜지스터 1 개, PRAM 셀 1 개) 구조의 시냅스를 사용하여, MNIST 숫자 인식을 목표로 한 3층 신경망 모의실험에서 95.5%의 인식률을 달성하였다고 발표하였다.

MRAM 기반의 시냅스는 미국 퍼듀대(Purdue University)에서 수년간 연구해 오고 있다. STDP 구현을 위해 스핀-궤도 토크(spin-orbit torque)를 활용하는 강자성체(ferromagnet)-중금속(heavy metal) 이종접합(heterojunction)을 제안하였는데, 이 소자의 장점은 스파이크 전달 통로와 프로그래밍 전류 통로가 달라서 온라인(online) 학습 시 신뢰성 있는 동작이 가능하다는 것이다. 이러한 이종접합을 확률론적(stochastic) 이진(binary) 시냅스로 사용하여 확률론적 STDP를 구현하고, 여기에 장기와 단기 기억을 갖는 시냅스를 조합하여 학습 안정화를 시도하여, MNIST 데이터에 대한 시스템 모의실험에서 STDP만을 사용한 학습을 통하여 70~80% 수준의 정확도를 달성하였다.

같은 그룹에서 MTJ를 스파이크 발생 뉴런으로 사용하는 연구도 진행되고 있으며, 대뇌 피질의 뉴런이 확률론적으로 스파이크를 발생시키는 것과 유사한 동작을 구현하고, 나아가 신념망(belief network)에서의 확률론적 연산 요소와 직접 대응시킬 수 있는 가능성에 대해서도 연구하고 있다.

중국 베이항대(北航大)에서는 수직 적층된 MTJ로 구성된 시냅스와 뉴런을 사용하는 전-스핀(all-spin) 심층신경망(DNN)을 제안하고, 이로부터 다단계 저항 상태와 다단계 전달함수를 구현하여, MNIST 손글씨 숫자 인식률을 90% 이상으로 끌어올렸다.

■ 산업 동향

인공지능 반도체 산업은 현재 태동기라고 할 수 있다. 아직 본격적인 시장이 형성되어 있지 않으며, 반도체 설계 및 제조 회사들이 시제품 또는 초기 제품을 출시하기 시작한 상태이다. 이들 시제품이나 초기 제품은 모두 CMOS에 기반한 1세대 인공지능 반도체 제품으로 소재 관점에서는 기존의 반도체 제품과 다를 것이 없고, 2세대 인공지능 반도체에서 새로운 소재가 본격적으로 도입되고 사용될 것으로 예상된다.

국내 기업들의 경우 주로 외국의 산업체, 대학들과의 기술협약으로 연구를 진행 중이며 본격적인 개발 및 상용화에는 이르지 못하고 있다. 반도체 패키징·테스팅 기업인 ‘네패스(Nepes)’는‘제너럴비전(General Vision)’과 기술협약을 맺고, 올해 576개의 뉴런을 내장한 국내 최초 뉴로모픽 칩을 생산하겠다고 발표하였다.

SK하이닉스의 경우 2016년 미국 스탠퍼드대, 램 리서치(Lam Research), 버슘 머티리얼즈(Versum Materials)와 함께 강유전체 물질을 활용한 ‘인공신경망 반도체 소자 공동 연구개발’ 협약을 체결하였고, 삼성전자의 경우 삼성종합기술원 산하 두뇌컴퓨팅 연구실을 중심으로 관련 연구가 진행 중이나, 실제 생산 및 상용화를 위한 본격적인 연구개발 단계는 아닌 것으로 보인다.

미국의 반도체 기업들은 시제품 또는 초기 제품을 출시하면서 인공지능 반도체 시장의 선점을 위한 노력을 경주하고 있다. IBM은 TrueNorth 시제품을 대학을 포함한 200여개 기관에 배포하여 다양한 응용에 사용해 볼 수 있도록 하는 테스트를 진행하고 있고, 퀄컴(Qualcomm)은 휴대용 단말기 응용 프로세서(application processor, AP)의 코프로세서(co-processor) 형태로 연결 가능한 신경처리장치(neural processing unit, NPU)인 Zeroth 개발을 통해 휴대 장비에서의 효율적인 인공지능 구현을 추구하고 있다.

구글(Google)은 자사의 오픈소스 프레임워크(open source framework)인 텐서플로우(TensorFlow)와 함께 사용되는 하드웨어로 텐서처리장치(tensor processing unit, TPU)를 개발하여 실제 인공지능 서비스에 사용하고 있으며, 인텔(Intel)은 Arria 10이라는 FPGA (field-programmable gate array) 기반의 딥러닝 가속기와 Movidius라는 시각처리장치(vision processing unit, VPU)을 개발하여 기존 CPU를 넘어 다가오는 차세대 인공지능 시장에 대비하고 있다.

중국의 화웨이(Huawei)에서도 최근 AP에 인공지능을 접목시킨 기린(Kirin) 970을 발표하였는데, 기린은 옥타코어(8-core) CPU와 12개의 차세대 GPU 코어로 구동되며, 10 nm의 새로운 공정을 활용해 55억 개의 트랜지스터를 1 cm²에 집적하였고, NPU 기능을 탑재하여 높은 에너지 효율을 제공하는 것으로 알려져 있다.

■ 미래 연구 방향 및 정책 제언

인공지능 반도체 1세대는 기존의 소재와 소자를 기반으로 한 집적회로이므로 연구 방향은 기존의 반도체 집적회로 관련 소재 연구와 크게 다르지 않을 것으로 보이지만, 소재와 소자의 근본적인 변화를 요구하는 인공지능 반도체 2세대에서는 그 빌딩블록인 인공 시냅스와 뉴런을 구성하기 위한 소재에 대한 연구가 매우 중요해질 것으로 예상된다. 특히 인공지능 반도체 2세대는 지금까지 반도체 집적회로의 주류였던 디지털 시스템에서 벗어나 아날로그적 특성이 중요한 새로운 컴퓨팅 시스템으로 바뀌는 패러다임 전환의 세대가 될 것으로 예상되므로, 소재의 특성에 대한 요구 사항이 크게 달라질 뿐 아니라, 새로운 소재와 소자에 대한 수요가 대폭 늘어날 것으로 보인다.

차세대 인공지능의 견인차가 될 인공지능 반도체 연구의 원활한 수행을 위하여 미국에서는 SyNAPSE, 유럽에서는 HBP, 중국에서는 CBP라는 국가 주도의 대형 프로그램을 수행하고 있는데 반해, 우리나라에서는 체계적인 로드맵이나 프로그램 없이 산발적이고 단기적인 소규모 과제로 이어나가고 있는 형편이다. 현재 우리나라는 삼성전자, SK하이닉스 등 반도체 기업이 글로벌 메모리 시장에서 우위를 차지하고 있다. 인공지능 반도체는 메모리-프로세서 융합체이다. 여기서 메모리는 단순한 기억장치로서 역할에서 벗어나 프로세서 간의 연결 강도를 결정하는 핵심적인 역할을 할 것으로 기대된다. 그러나 우리나라가 이러한 패러다임 변화에 적절히 대응하지 못한다면 향후 메모리 시장의 점유율 감소는 물론, 반도체 시장 전반의 점유율 감소로 이어질 것이다. 다행히 인공지능 반도체 산업은 이제 막 태동기에 있으며, 특히 소재와 소자에 중점이 있는 2세대 인공지능 반도체는 아직 초기 연구 단계에 있으므로, 메모리 강국인 우리나라에서 로드맵과 장기적인 전략을 만들고 관련기업의 적극적인 참여를 이끌어 낸다면 인공지능 하드웨어 분야에서도 세계를 선도하는 국가로 나아갈 수 있을 것이다.

▲ <그림 3-3-2-13>플로팅 바디 시냅스 트랜지스터(floating-body synapse transistor, FST) : (a)개략도, (b)A-A’ 단면을 잘라서 본 전자현미경 사진

▲ <그림 3-3-2-13>플로팅 바디 시냅스 트랜지스터(floating-body synapse transistor, FST) : (a)개략도, (b)A-A’ 단면을 잘라서 본 전자현미경 사진 ▲ <그림 3-3-2-14>RRAM의 구조 : (a)선택 소자가 없는 경우, (b)선택 소자를 포함한 경우

▲ <그림 3-3-2-14>RRAM의 구조 : (a)선택 소자가 없는 경우, (b)선택 소자를 포함한 경우 ▲ <그림 3-3-2-15>PRAM의 구조와 저항 상태 : (a)낮은 저항 상태, (b)높은 저항 상태

▲ <그림 3-3-2-15>PRAM의 구조와 저항 상태 : (a)낮은 저항 상태, (b)높은 저항 상태 ▲ <그림 3-3-2-16>자기 터널 접합(MTJ) : (a)낮은 저항 상태, (b)높은 저항 상태

▲ <그림 3-3-2-16>자기 터널 접합(MTJ) : (a)낮은 저항 상태, (b)높은 저항 상태 ▲ <그림 3-3-2-17>흥분성과 억제성 시냅스 동작을 위한 두 개의 전류 거울을 갖는 적분-발화 뉴런 회로. 커패시터 C1을 이용하여 입력 전류를 적분한다.

▲ <그림 3-3-2-17>흥분성과 억제성 시냅스 동작을 위한 두 개의 전류 거울을 갖는 적분-발화 뉴런 회로. 커패시터 C1을 이용하여 입력 전류를 적분한다. ▲ <그림 3-3-2-18>커패시터 대신 RRAM을 사용한 적분-발화 뉴런 회로

▲ <그림 3-3-2-18>커패시터 대신 RRAM을 사용한 적분-발화 뉴런 회로